IBM anunció la semana pasada que ha desarrollado la capacidad de proporcionar transistores de 2nm a los chips. La situación actual con las bellas artes es generalmente alrededor de 5nm o 7nm, por lo que es un gran salto, a pesar de que evaluar tamaños entre diferentes fabricantes no siempre es correcto.

Más llamativo que su tamaño es que estos chips probablemente se desarrollarán con un supuesto plan de 'nanohoja'. La mayoría de los transistores elegantes se basan fundamentalmente en 'FinFET', el lugar en el que los flujos de corriente a través del semiconductor se extienden directamente hacia arriba en un equilibrio. Los transistores Nanosheet o 'gate-all-around' convierten este balance directamente en una pila de tiras individuales específicas, y el plan debería poder mejorar la eficiencia energética y permitir que los diseños cambien más esencialmente las propiedades eléctricas de diferentes partes del chip. . FinFET ha sido estándar desde 2011, por lo que mostrar una nueva versión de semiconductores de plástico es un cambio sensiblemente grande en el mundo de los semiconductores.

En un salto adelante significativo, IBM anunció el primer chip de 2 nm de su tipo basado en la innovación de nanoláminas. La organización dijo que este chip ayudaría a avanzar en el negocio de los semiconductores y tomaría en cuenta su interés en desarrollo de chips. Los procesadores de 2 nm pueden cuadruplicar la duración de la batería de las PDA. Con un uso normal, la batería del teléfono puede durar hasta cuatro días. El chip ofrece un 45 % mejor y utiliza un 75 % menos de energía que los chips de nodo de 7 nm más excepcionales actuales.

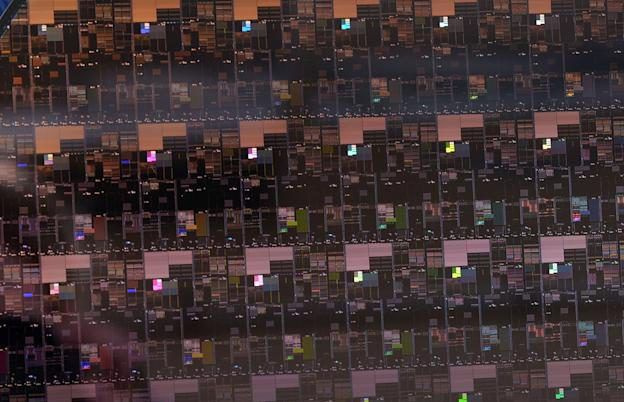

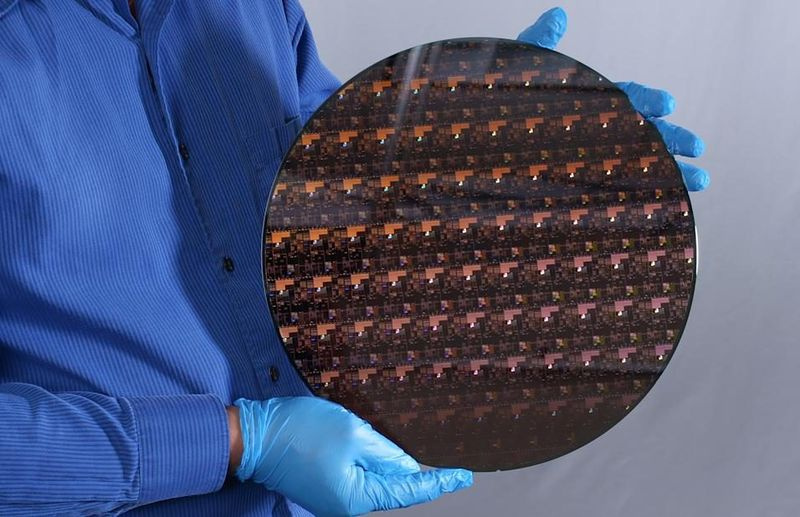

La combinación de fuerza/ejecución acelera el giro de los acontecimientos y la transmisión de las etapas informáticas intelectuales, de borde y otras de vanguardia transmitidas a través de condiciones de nube cruzadas y pedales de acelerador de cifrado trabajados para trabajar con PC cuánticas. La nanotecnología de 2nm puede incluir hasta 50 mil millones de transistores en un chip del tamaño de una uña. Más transistores en un chip permitirán a los creadores desarrollar para impulsar responsabilidades de vanguardia como IA, computación en la nube, seguridad aplicada por hardware y encriptación.

La nueva contribución de IBM aún se encuentra en la etapa de verificación de la idea y podría pasar algún tiempo antes de que esté disponible comercialmente. En este momento, las organizaciones adversarias de IBM, Samsung y TSMC, están entregando chips de 5 nm en sus fundiciones. TSMC había declarado anteriormente que comenzará a entregar chips de 4nm antes de fines de 2021 y producirá chips de 3nm continuamente el 50% de 2022. Los chips de 7nm de Intel aún están en desarrollo.

¿Cómo se le ocurrió a IBM?

El término nanohoja se creó por primera vez en los laboratorios de IBM en 2012 cuando su equipo de especialistas se ocupaba de la ingeniería de otro dispositivo. El objetivo era construir una opción adecuada para la estructura convencional de nanocables. El segundo Eureka de IBM acompañó la ingeniería de nanoláminas, que ofreció las ventajas electrostáticas de los nanocables junto con el grosor necesario para un mejor rendimiento.

Con esta combinación de aspectos destacados, las nanoláminas conquistaron FinFET, una estructura de semiconductores predominante en ese momento. En cualquier caso, el negocio estaba superando rápidamente el plan FinFET. Los planificadores intentaron empacar más transistores, pero eso provocó un derrame de semiconductores.

La innovación FinFET recibe su nombre de la construcción FET y se asemeja a un montón de cuchillas. En esta construcción, los electrones pasan a través de delicadas láminas verticales, en lugar de una superficie nivelada, para atravesar los transistores. Por otra parte, las nanoláminas apilan transistores uno encima del otro para dar forma a diseños en capas. El principal semiconductor de 2 nm es el nuevo dispositivo de voltaje de umbral múltiple (Multi-Vt) con niveles de derrame que cruzan tamaños de tres órdenes. Permite a los fabricantes elegir un grado superior de ejecución.